# Data Driven Study of Systematic Variation of Transistor Characteristics from High Volume Wafer Fabrication

Micron Mentors: Andrew Scott, Chris Petz, Cynthia Atanga, Dibao Zhou, UW Advisor: Luna Huang Department of Materials Science and Engineering, University of Washington, Seattle, Washington

#### **Introduction and Challenges**

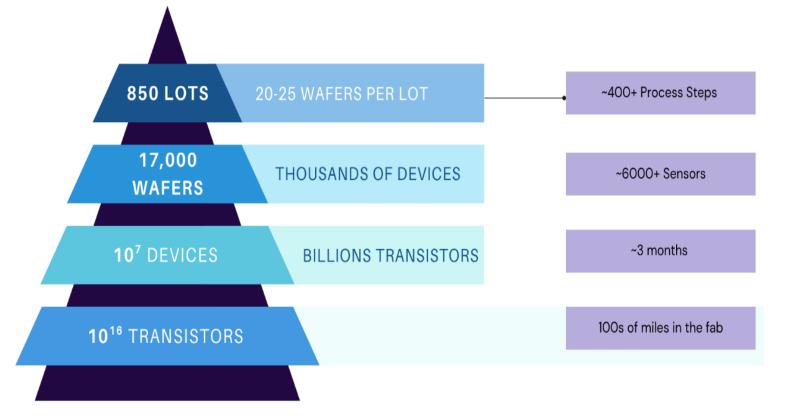

Wafer processing is a critical phase in semiconductor manufacturing, where silicon wafers undergo physical and chemical treatments to produce integrated circuits. Ensuring high yield and quality in this process is essential, as wafer defects can result in significant financial loss and delays. However, early failure detection is challenging due to the high dimensionality of process data and the difficulty of linking specific variables to final outcomes.

Threshold voltage—the minimum gate voltage needed to activate a transistor—is a key indicator of wafer quality, affecting performance, power efficiency, and reliability. It can reveal defects in doping, oxide thickness, and other fabrication steps. By analyzing sensor data collected throughout processing, we aim to **identify which** process parameters most significantly impact variations in complementary metaloxide-semiconductors (CMOS) threshold voltages.

**Figure 1:** Complexity of high-volume wafer production

### **Data Processing Decisions**

- **Duplicates:** Kept the latest measurement per parameter; averaged values at identical timestamps

- Restructuring: Reformatted data so each row is a single wafer, with columns corresponding to a specific measurement.

- Imputation: Filled missing values using data from wafers in the same lot.

- Train/Test Split: Chronologically split data to preserve production time order

#### **Model Choice ≫**NIXTLA CatBoost LSTM TimeGPT Quality Predictive **Early Detection** Enhancement Maintenance Spots issues early mproves produc redicts equipmer across the uality with real-time failures through AI production line sensor data technologies

- •TimeGPT: Forecasts long-term wafer trends to predict maintenance and reduce downtime

- •LSTM: Uncovers temporal patterns across process steps to predict early wafer failure

- •CatBoost: Identifies key parameters affecting yield for early detection and optimization

- •**Together:** Enable an Al-driven framework for smarter, more reliable, and efficient manufacturing

Figure 2: Leveraging TimeGPT, CatBoost, and LSTM for Smarter Semiconductor Manufacturing

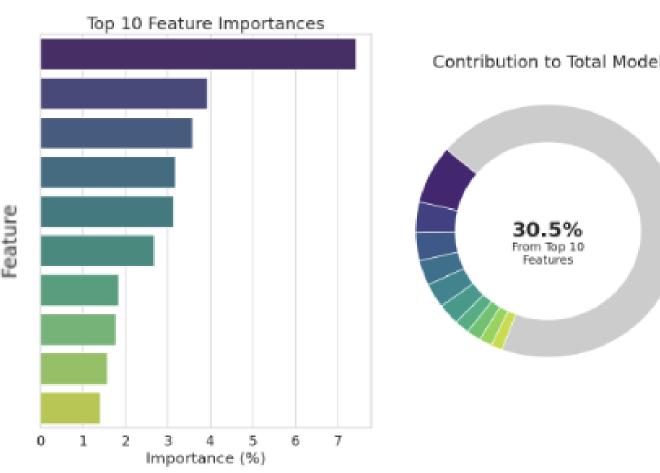

#### **Feature Importance**

- Analyzed CatBoost feature importance scores to rank input parameters by relevance (see Figure 3)

- Applied recursive feature elimination to remove less relevant features and reduce signal to noise ratio

- Identified 55 key features that yielded the best predictive performance

Figure 3: Feature importance and contribution to model

### **Analyzing Results**

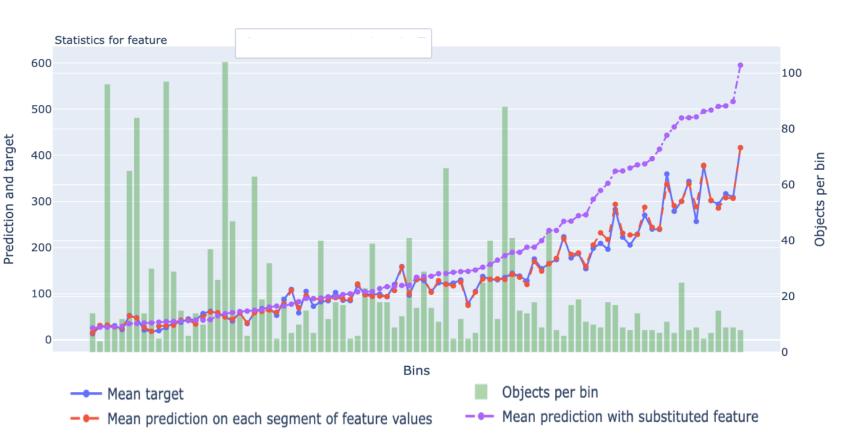

- Used catplots (see Figure 4) to visualize how key features relate to threshold voltage predictions

- Revealed trends that explain how specific parameters drive variation

- Enabled root cause identification and more targeted process improvements

- Informed practical recommendations to refine process steps linked to failure, improving yield and consistency

Figure 4: Example catplot

## Conclusion

- Successfully identified 55 key process steps influencing device performance

- Validated findings with Micron engineers, confirming their real-world relevance

- LSTM and TimeGPT showed great potential in capturing temporal patterns in complex manufacturing data

- These models offer broad applicability across semiconductor manufacturing challenges

Figure 5: Team and Micron mentors at Boise, ID headquarters